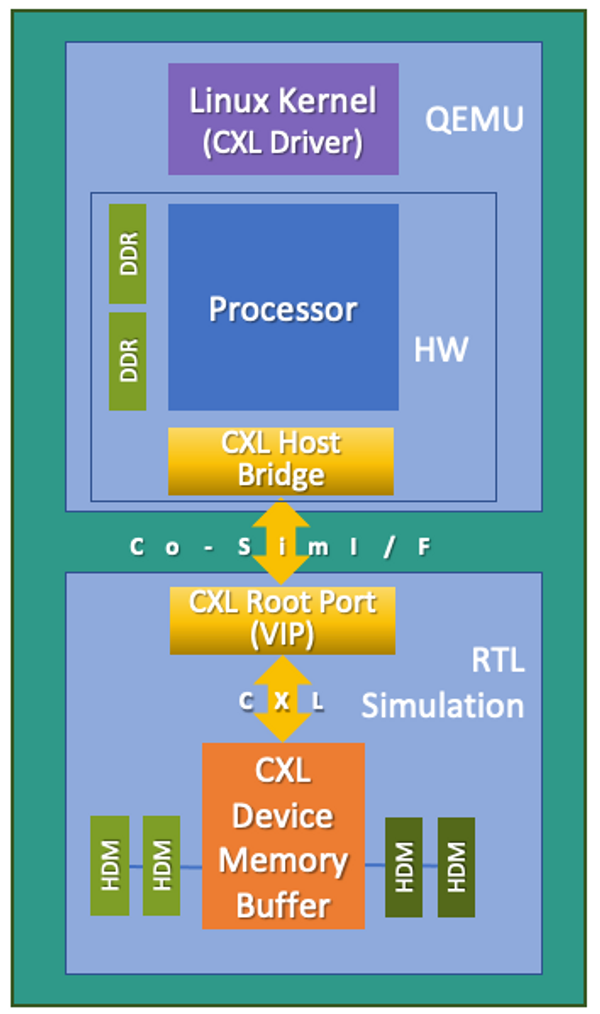

Tewksbury, MA., April 15, 2021 — Avery Design Systems, a leader in functional verification solutions, today announced its CXLTM 2.0 system-level simulation solution. The comprehensive offering supports the co-simulation of a CXL-aware Linux kernel and QEMU x86 virtual host system emulator with its SystemVerilog CXL Host VIP. The solution enables pre-silicon hardware-software validation of CXL 2.0 Type 3 memory expansion system designs, accelerating development time and providing an efficient approach to customization and application development for systems using the CXL 2.0 interface standard

“QEMU-CXL co-simulation creates the most complete and accurate representation of the CXL-enabled reference system environment from which to verify CXL 2.0 Type 3 SoC hardware RTL and software,” said Chris Browy, Vice President Sales and Marketing at Avery Design Systems. “Early integration of the actual hardware and software enables pre-silicon co-verification and rigorous compliance testing that accelerates the development schedule and dramatically reduces bug fix times and iterations.”

Avery is a contributor to the Compute Express LinkTM (CXL) Compliance Working Group and has deployed the QEMU-CXL co-simulation solution with the Compute Express Link (CXL) Compliance Software Subgroup to support test suite development for the CXLCV 1.1 compliance tool with plans to also support future CXL 2.0 efforts.

“As an early CXL Consortium member, Avery has contributed its SoC verification expertise to advance the development of the CXL compliance program,” said Barry McAuliffe, CXL Consortium President. “It is great to see this innovative technology come together in support of a fast-growing CXL ecosystem.”

Co-simulating the SoC RTL with a QEMU open software virtual machine emulator environment running the latest Linux 5.12-rc2 kernel allows software engineers to natively develop and build custom firmware, drivers, and applications and run them unaltered as part of a comprehensive system-level validation process using the actual SoC RTL hardware design. In a complementary manner, hardware engineers can evaluate how the SoC performs through executing UEFI and OS boot and custom driver initialization sequences in addition to running real application workloads and utilize the CXL protocol aware debugging features of the VIP to effectively investigate any hardware related issues.

The QEMU-VIP co-simulation solution supports PCIe®, CXL, and AMBA including AXI, AXI-Stream, AHB, and APB and can address system simulation of both host and embedded processing environments.

Avery Design Systems

Founded in 1999, Avery Design Systems, Inc. enables system and SOC design teams to achieve dramatic functional verification productivity improvements through the use of formal analysis applications for gate-level X-pessimism verification and real X root cause and sequential back tracing; and robust core-through-chip-level Verification IP for PCI Express, CXL, CCIX, Gen-Z, USB, AMBA, UFS, MIPI CSI/DSI, I3C, DDR/LPDDR, HBM, ONFI/Toggle/NOR, NVM Express, SATA, AHCI, SAS, eMMC, SD/SDIO, CAN FD, and FlexRay standards. The company has established numerous Avery Design VIP partner program affiliations with leading IP suppliers. More information is available at www.avery-design.com.

###

Compute Express Link and CXL are trademarks of the CXL Consortium

PCI Express and PCIe® are trademarks of PCI-SIG